D Flip Flop Truth Table

When D 1 and CLOCK HIGH. Logic diagrams and truth tables of the different types of flip-flops are as follows.

What Is Flip Flop Circuit Truth Table And Various Types Of Flip Flops

During the rest of the clock cycle Q holds the previous value.

. In SR NAND Gate Bistable circuit the undefined input condition of SET 0 and RESET 0 is forbidden. The upper NAND gate is enabled and the lower NAND gate is disabled when the output Q To is set to 0. When a triggering clock edge is detected Q D.

We can summarize the behavior of D-flip flop as follows. Both the JK flip flop inputs are connected as a single input T. Force both outputs to be 1.

Truth Table of T flip flop. The truth tables for the flip flop conversion are given below. But their values at the time of the PGT determine the output according to the truth table.

There are many applications where separate S and R inputs not required. In these cases by creating D flip-flop we can omit the conditions where S R 0 and S R 1. Analysing the above assembly as a three stage structure considering previous stateQ to be 0.

It means that the latchs output change with a change in input levels and the flip-flops output only change when there is an edge of controlling signalThat control signal is known as a clock signal Q. The table is then completed by writing the values of S and R. Make the flip flop in set state Q1 the trigger passes the.

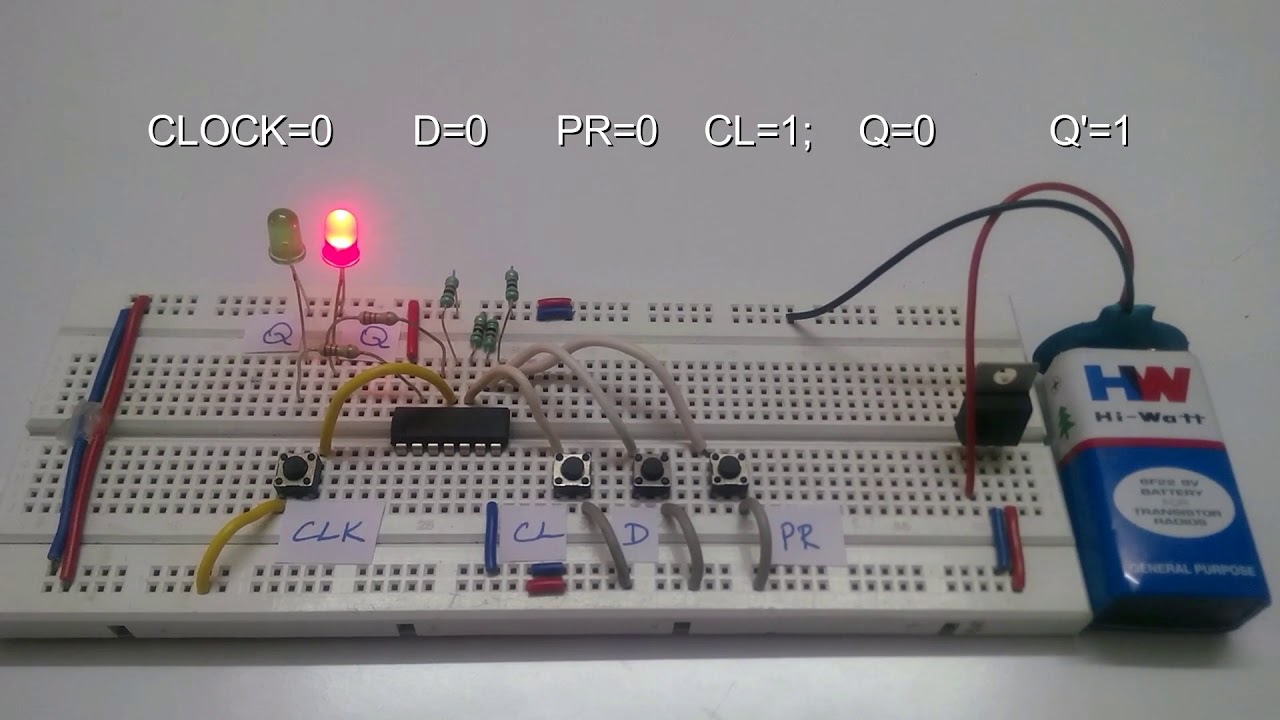

Again starting with the module and the port declarations. D Flip Flop. Behavioral Modeling of D flip flop.

In D flip-flop if D 1 then S 1 and R 0 hence the latch is set on the other hand if D 0 then S 0 and R 1 hence the latch is reset. Below is the logical circuit of the T flip flop which is formed from the JK flip flop. Output reg q qbar.

Q 1 Q 0. Draw the truth table of the required flip-flop. Qp1 simply suggests the future values to be obtained by the JK flip flop after the value of Qp.

This is an application of the versatile J-K flip. Write the corresponding outputs of sub-flipflop to be used from the excitation table. It is the drawback of the SR flip flop.

If J and K are different then the output Q takes the value of J at the next clock edge. S-R Flip Flop. This is known as a Gated D Latch.

It has the input- following character of the clocked D flip-flop but has two inputstraditionally labeled J and K. Thus comparing the NAND gate truth table and applying the inputs as given in D flip-flop truth table the output can be analysed. Drake Milligan is a country music artist whose songs Sounds Like Something Id Do and Kiss Goodbye All Night gained popularity after competing on Americas Got Talent TV 2 days ago.

Digital flip-flops are memory devices used for storing binary data in sequential logic circuitsLatches are level sensitive and Flip-flops are edge sensitive. Module dff_behaved clk q qbar. Lose the control by the input which first goes to 1 and the other input remains 0 by which the resulting state of the latch is controlled.

Override the feedback latching action. The present state is represented by Qp and Qp1 is the next state to be obtained when the J and K inputs are applied.

Flip Flop Conversion State Diagram Flop Flipping

T Flip Flop Circuit Truth Table And Working Electronic Circuit Projects Electronics Circuit Circuit Projects

D Flip Flop Circuit Truth Table Working

Ece 2610 D Flip Flip With Sr Flip Flip Included Diagram Logic Symbols

Comments

Post a Comment